SMAコネクタ-PCB接続部の特性改善

Table of Contents

1. 概要

SMA(Sub Miniture type A)コネクタ1はほどよく小さく,ほどよく性能が良いためマイクロ波帯の同軸コネクタとしてよく使われています. SMAコネクタは規格上18 GHzまで使える2ことになっています. しかし,コネクタ-回路間の構造変換部分をきちんと設計しないとその不連続性により反射が大きくなり,高周波帯で本来の性能を発揮することができません. 一方で同軸コネクタ自体は単純な構造であるためこの部分をしっかりとケアできれば1個数十円の安価なコネクタでも数千円を越える高級なコネクタと遜色無い特性を実現できます. そこで今回はSMAコネクタとプリント基板(PCB)上の伝送線路の接続部分の特性改善について考えます.

2. 悪い例

普段使いの安価なSMAコネクタはハンダ付けする芯線部分のピンの直径が1 mm程度あり,推奨フットプリントではこの部分のパッド幅が1.5 mmとなっています.

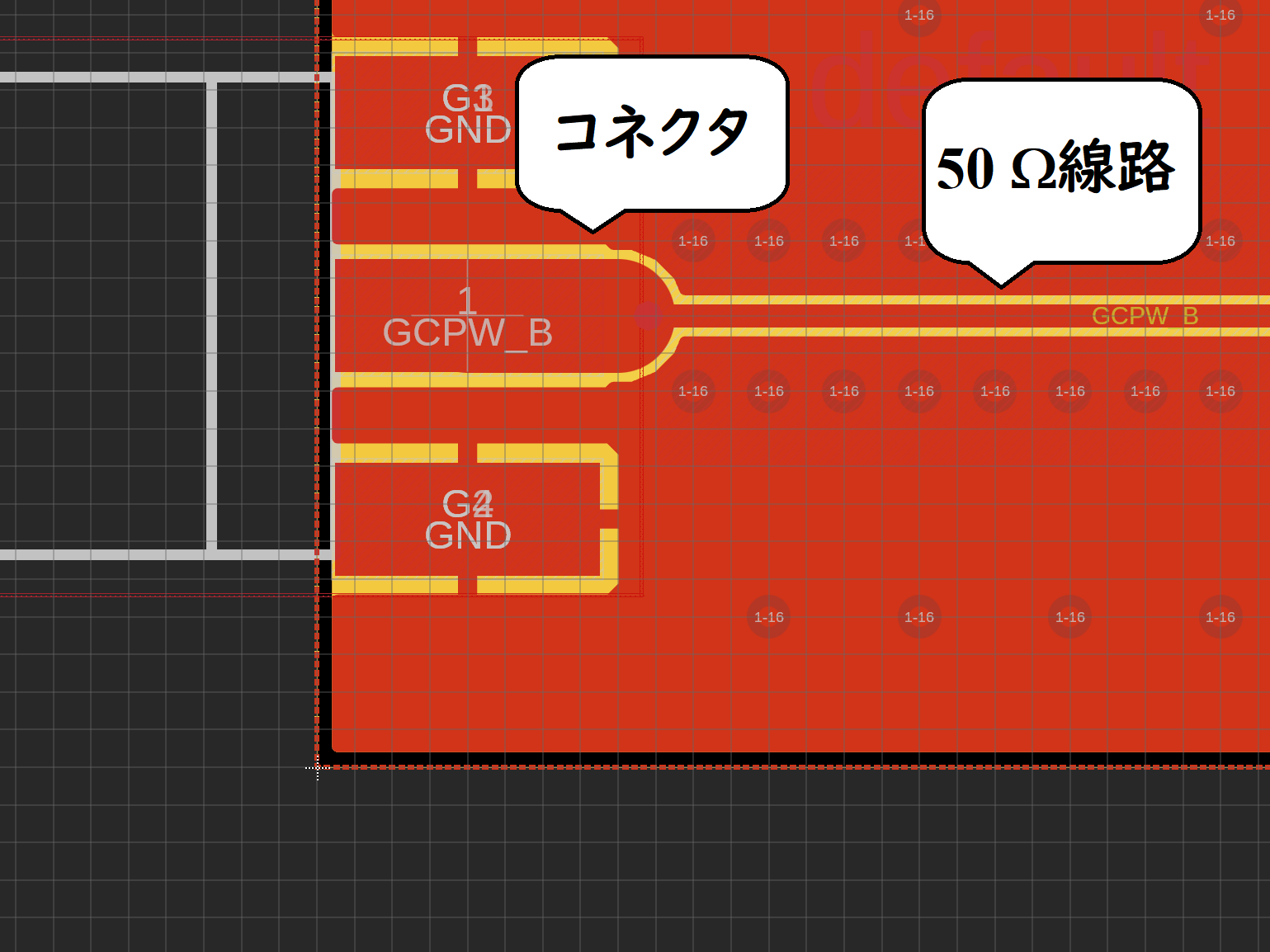

このコネクタと,線路幅の狭い伝送線路を以下のように何も考えずに繋ぎました.

見るからに反射が大きそうです.

とはいえこのセンターピン部分の長さは高々数mm程度です.実際どこまで特性が悪化するのでしょうか?

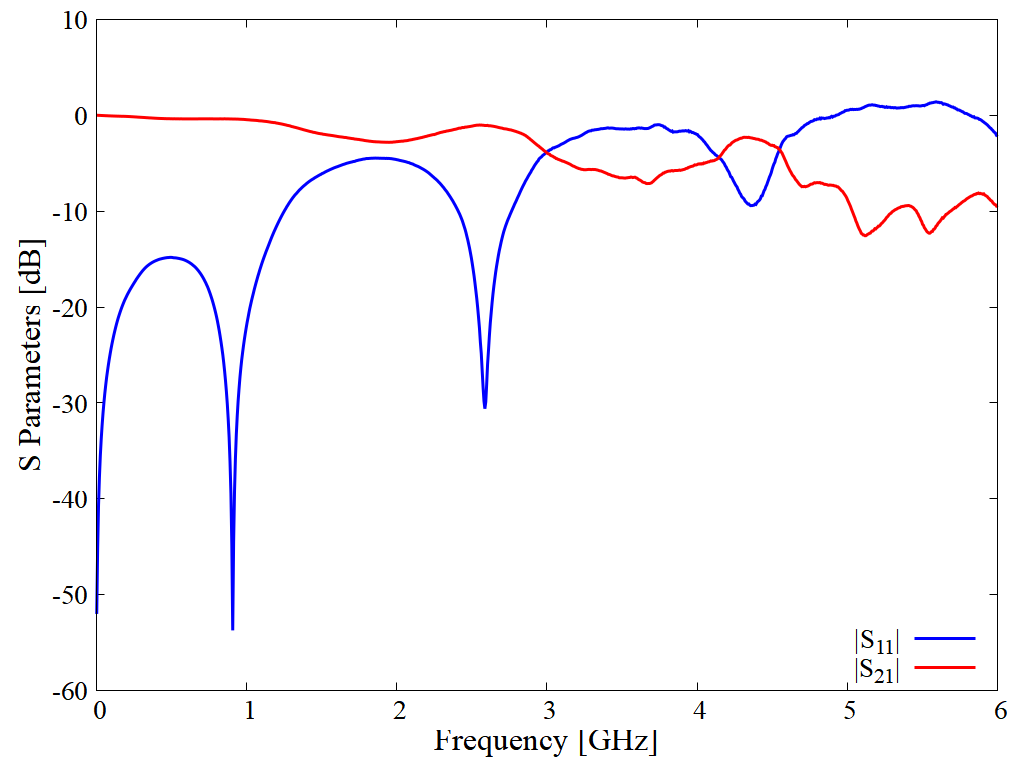

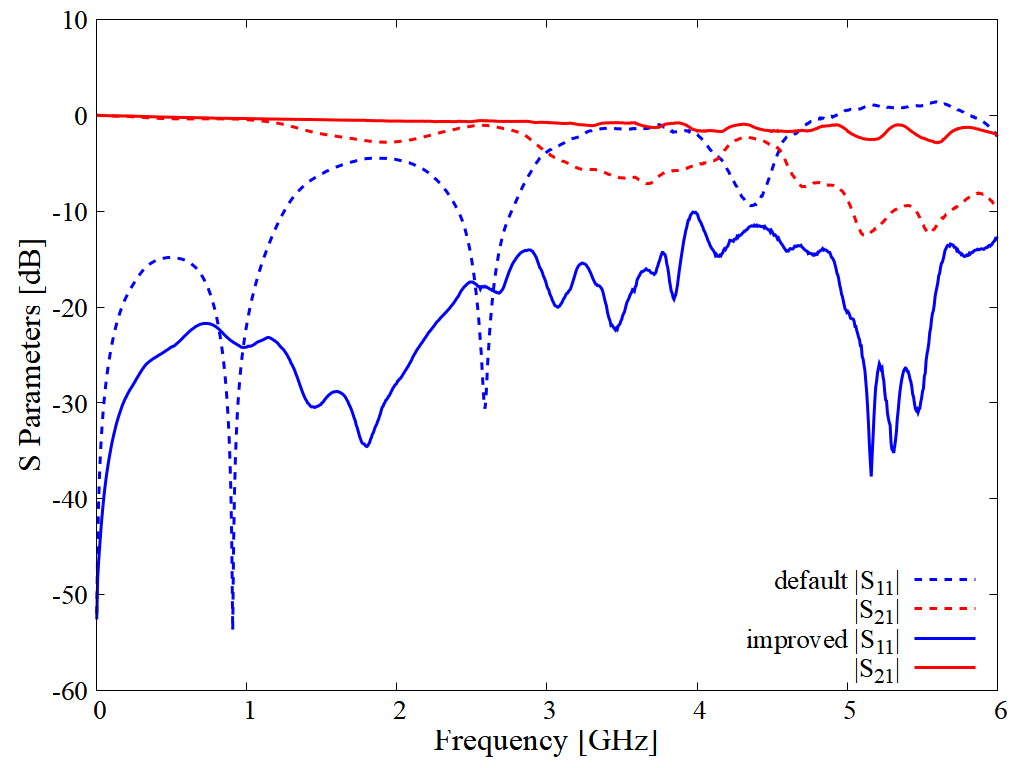

ということでPCB上の伝送線路(線路長50 mm)の両端になにも考えずSMAコネクタを付けた基板を試作し実測したところ以下のような結果3が得られました.

さて,おわかりいただけたでしょうか? アマチュア無線で使うような数百 MHz帯以下ではまあ許せそうな気もしますが,GHz帯ではかなり反射が大きいことが見てとれます. 例えばGPSで使われるような1.5 GHz付近ではかなり挿入損失が大きくなっており,宇宙からの微弱な信号を受信すると考えると無視できないかと思います. また,今回は2.4 GHz付近にたまたま反射零点があり,このあたりはかなり特性が良さげではありますが3 GHzあたりでは反射>通過となっておりもはやローパスフィルタのようになってしまっています. ここでは6 GHzまでしか測定できていませんが,6 GHzの時点で\(S_{21}\)が-10 dB程度と入力された電力の1割ほどしか伝わっておらずお話になりません.

3. なにが悪い

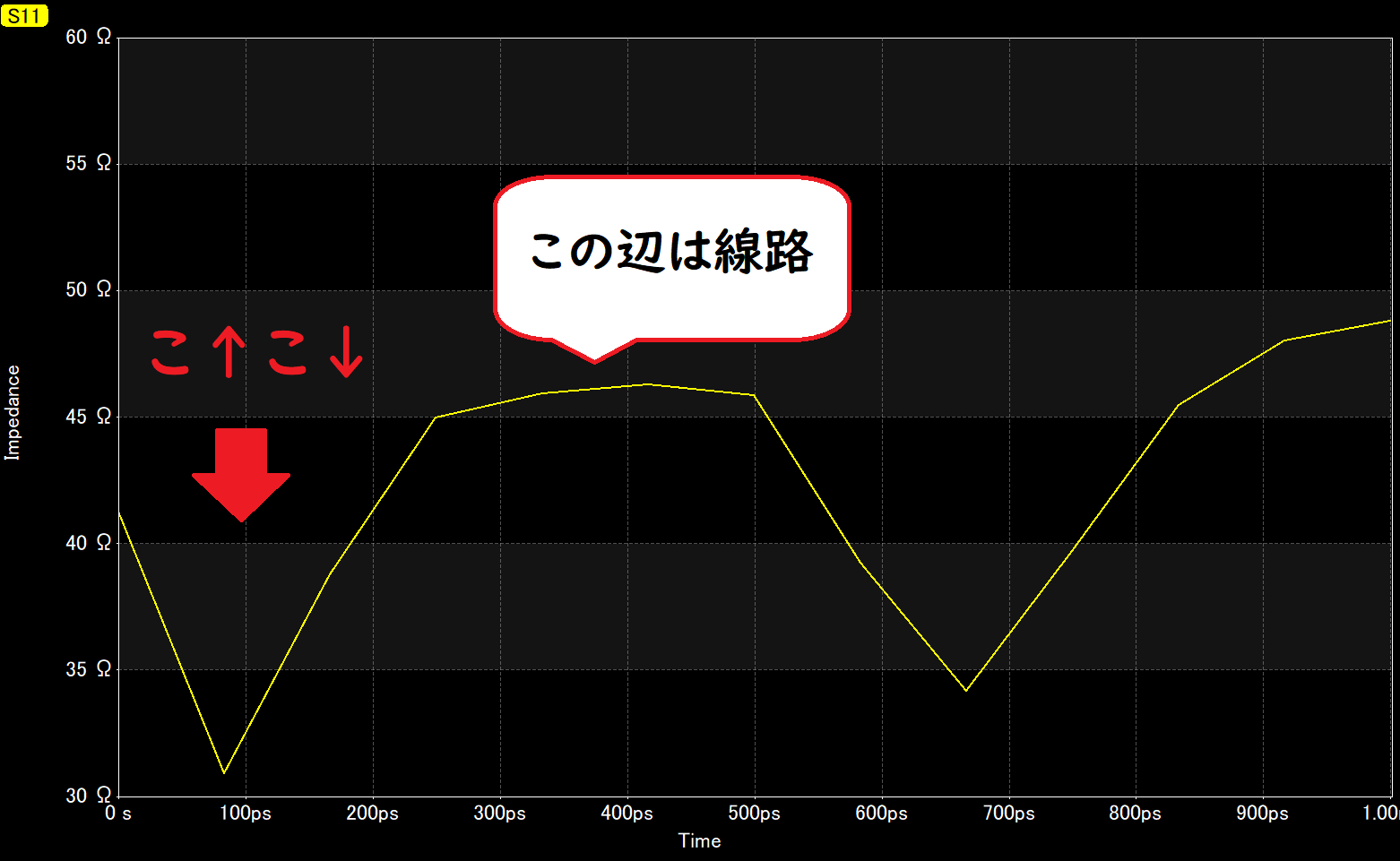

おしえて,僕は何処を直せばいい?ずっと探していた……のですがこれは周波数領域の\(S_{11}\)を逆フーリエ変換し,時間領域の反射係数に換算して考えると見えてきます.

このような手法をTDR(Time Domain Reflectmetry)と呼びます.

さて,測定したデータをいろいろと処理4すると以下のような時間-インピーダンスのグラフが得られます.

すっげえインピーダンス下がってる.はっきりわかんだね.

ということでコネクタ-PCB上の伝送線路のトランジション部分で特性インピーダンスがかなり下がって容量性が優位になっていることがわかります. この要因としてパッドが広すぎる(50 Ω線路幅が0.29 mmに対して1.5 mm)ことでキャパシタンスが増えていることと, コネクタのセンターピンの分導体厚が増してインダクタンスが減っていることが原因だと考えられます.

4. 対策と設計

ここでは,↑の実測結果から浮かび上がってきた問題点に対する対策の一例を紹介します. 他の種類の線路などより詳細な設計例についてはコネクタメーカーのアプリケーションノート5などもかなり参考になるので併せてご確認ください.

4.1. 伝送線路

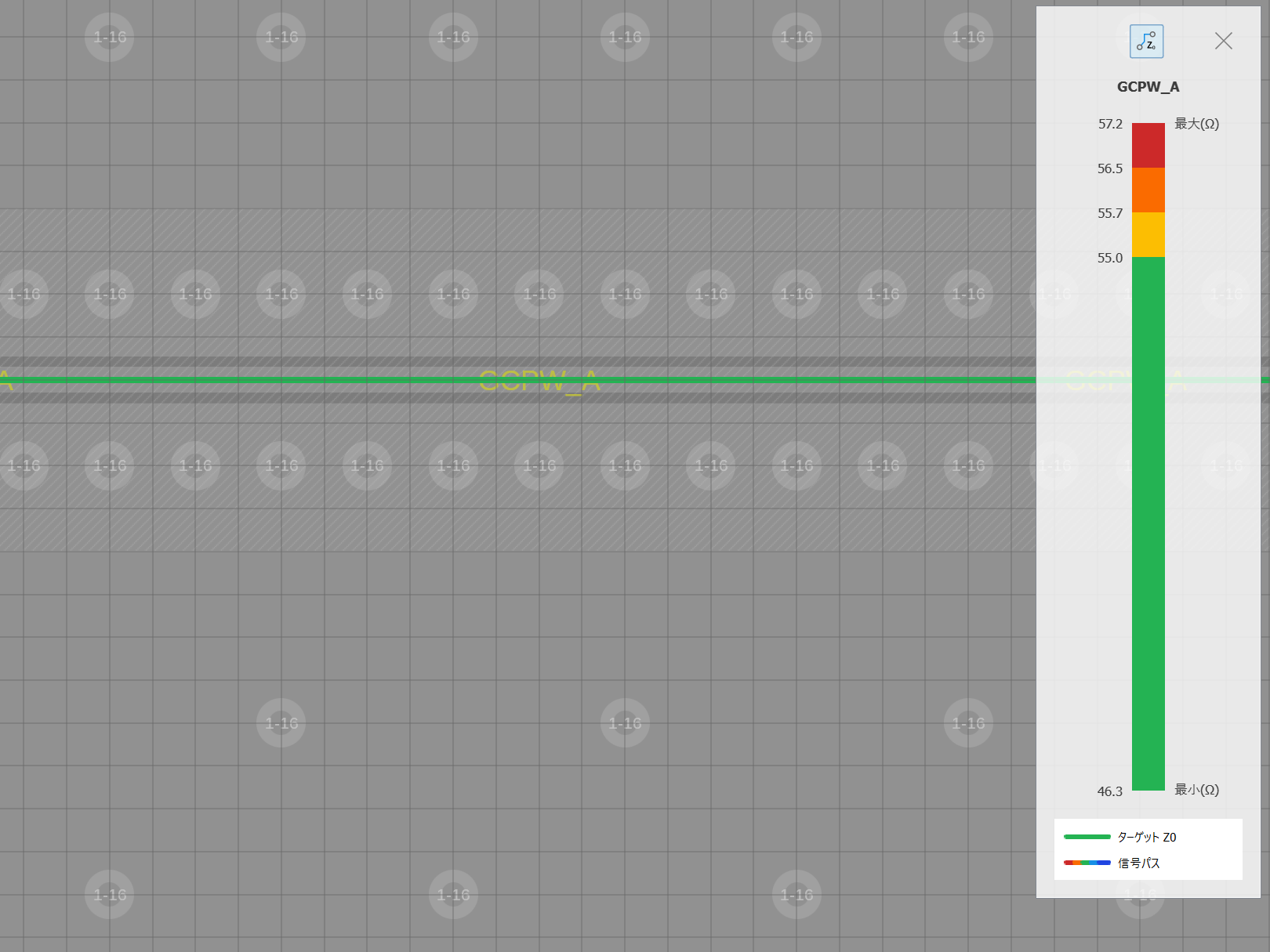

そもそもPCB上の伝送線路部分の特性インピーダンスがズレていては,どんなにコネクタを改良しても無駄です. ということで一応,伝送線路の特性インピーダンスも確認しておきます. 今回はJLCPCBで安価に製造できる4層基板(JLC04081H-7628 Stackup)を想定して設計を行いました. この層構成のうち2層目(inner Layer2)をベタGND層とし,表層(Top Layer1)にGND付きコプレーナ線路(GCPW)を引きます.

GCPWの特性インピーダンスの計算ツールは弊サイト内にもあるのですが,

この層構成の場合L1-L2間が0.2104 mmのプリプレグと層間が薄いため銅箔厚を無視するとやや計算がズレてきます.

ということで今回は電磁界シミュレータ6なども使いつついい感じに調整を行いました.

最終的にはG-S間隔をデザインルール最小の5 mil(0.127 mm)として,線路幅を11.5 mil(約0.29 mm)としました.

線路幅をそんなに細かく刻んでも結局エッチング時にそれなりの誤差が乗りそうな気もしますが……まあ良しとします.

4.2. SMAコネクタのフットプリント

さて,今回使用するSMAコネクタのフットプリントではセンターピン部分のパッド幅が1.5 mmとなっています.

50 Ω線路の幅が0.29 mmということを考えるとンアーッ!フットプリントがでかすぎます!!という感じがしますね.

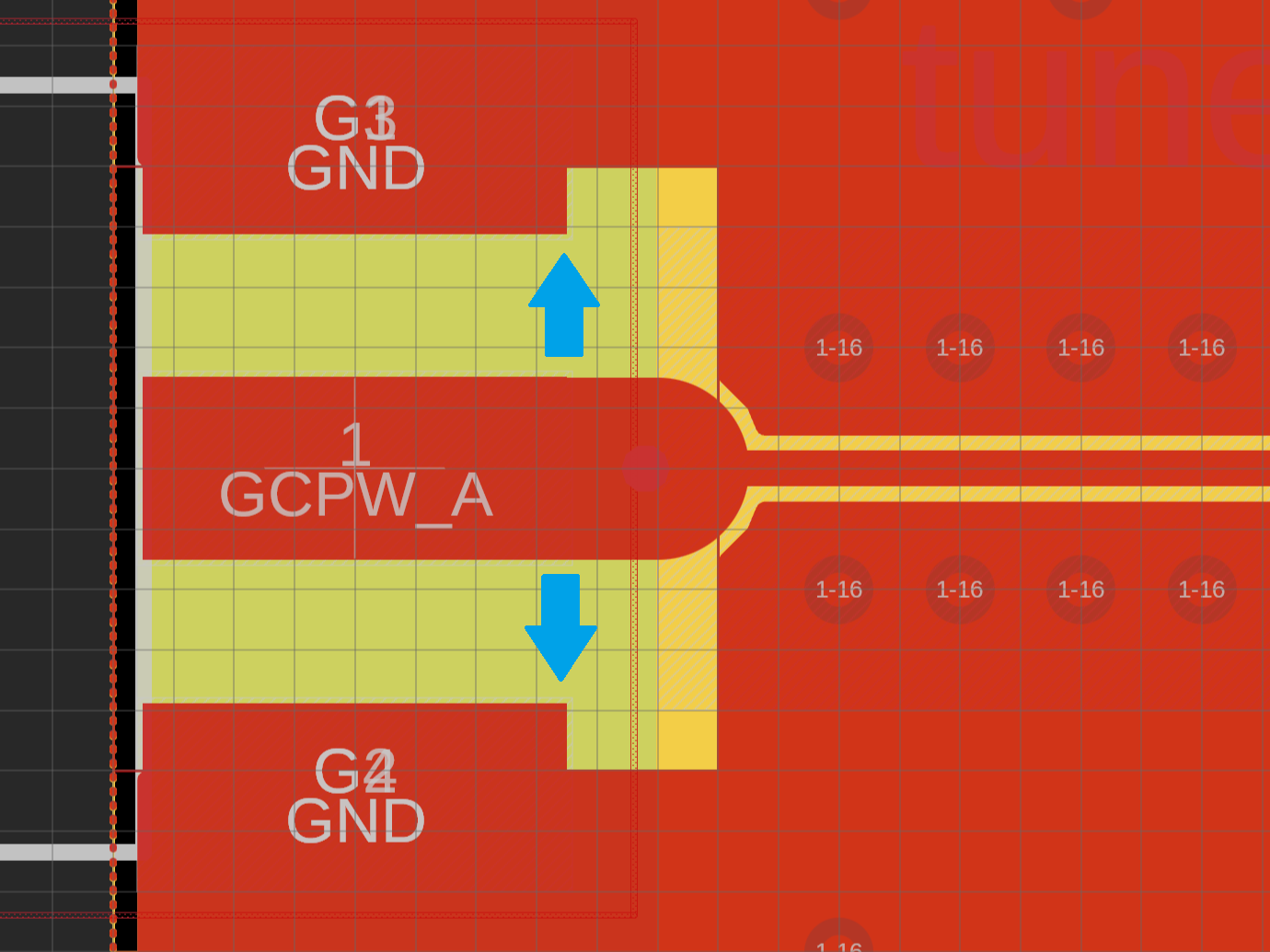

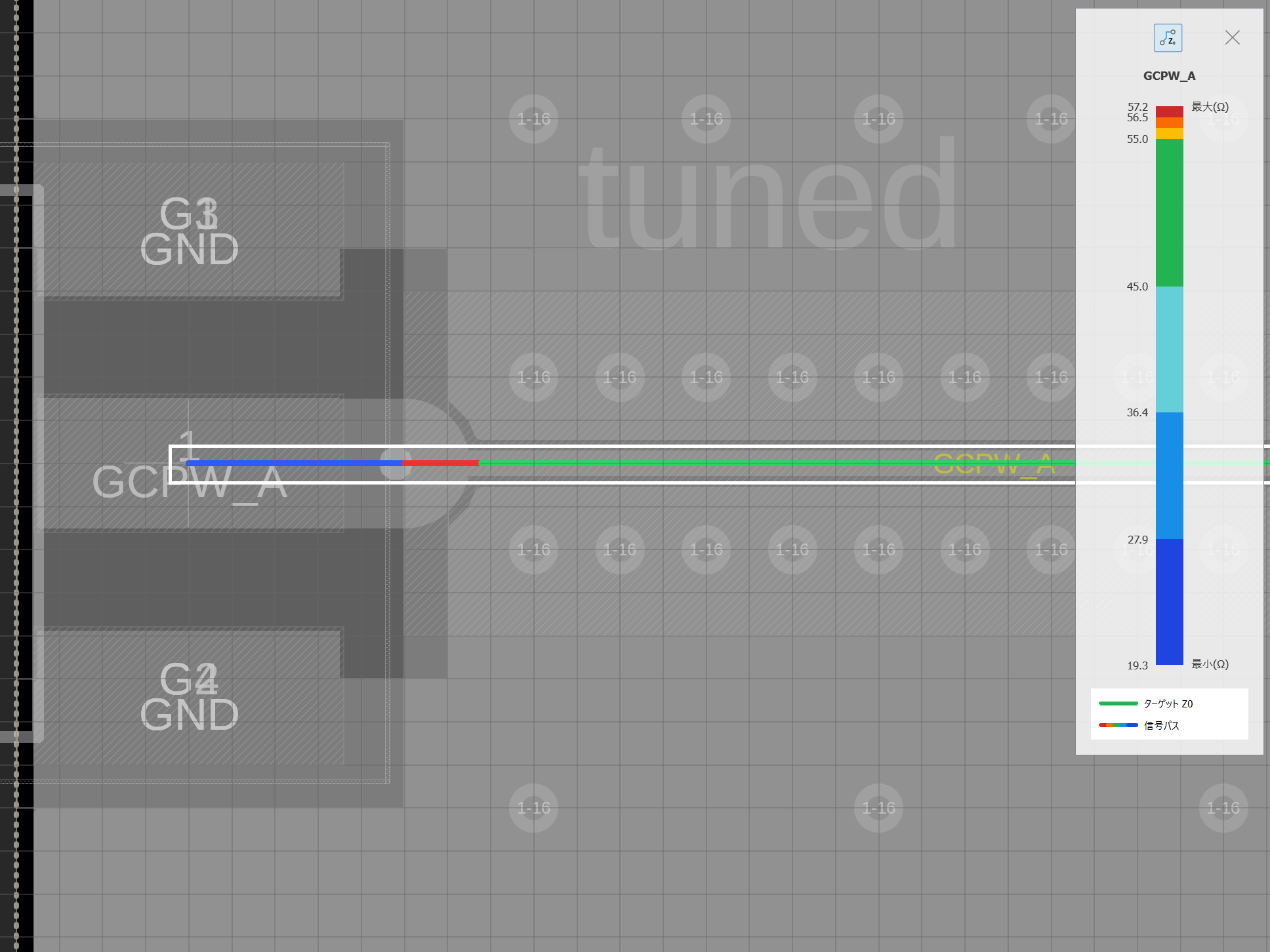

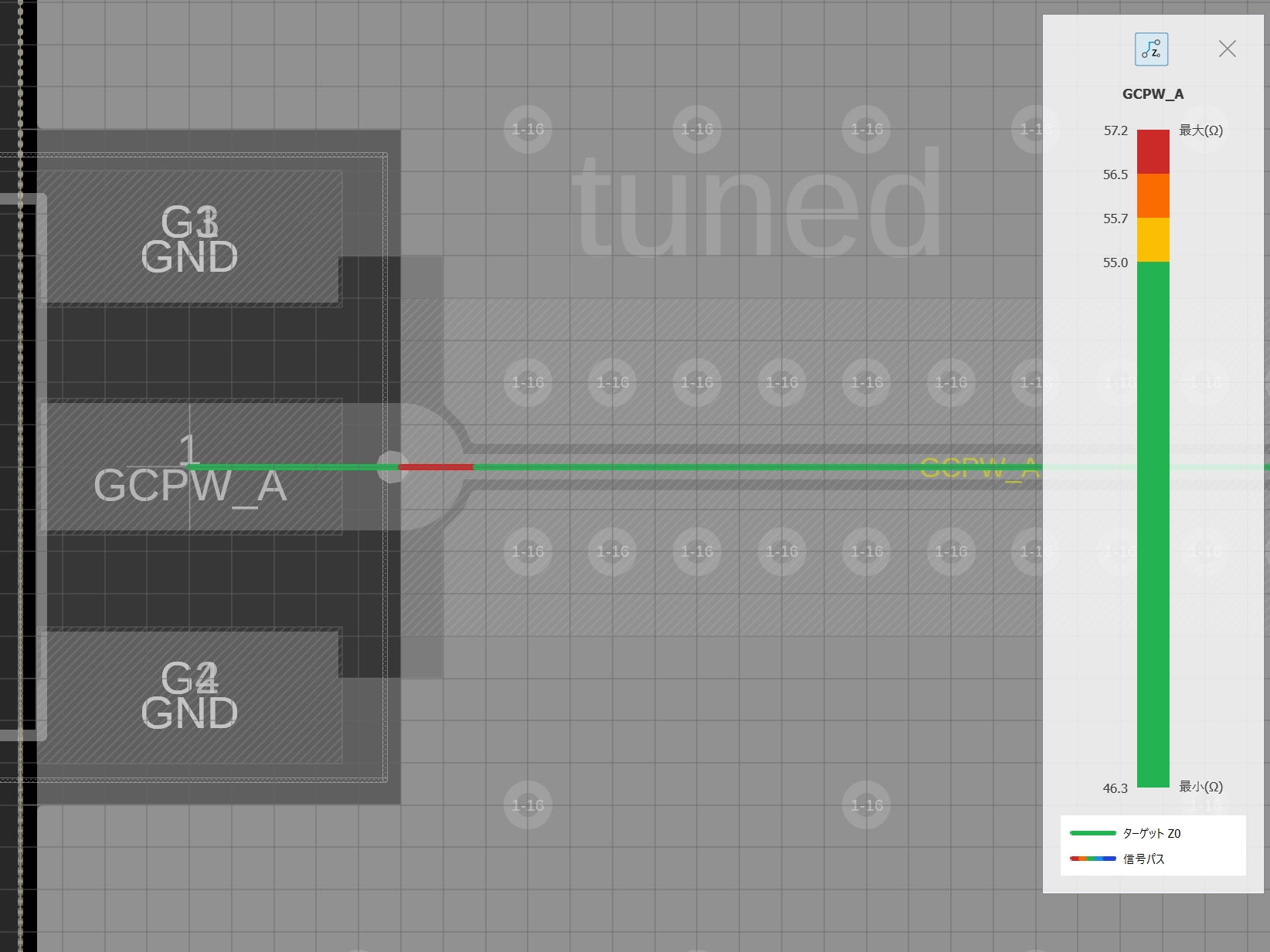

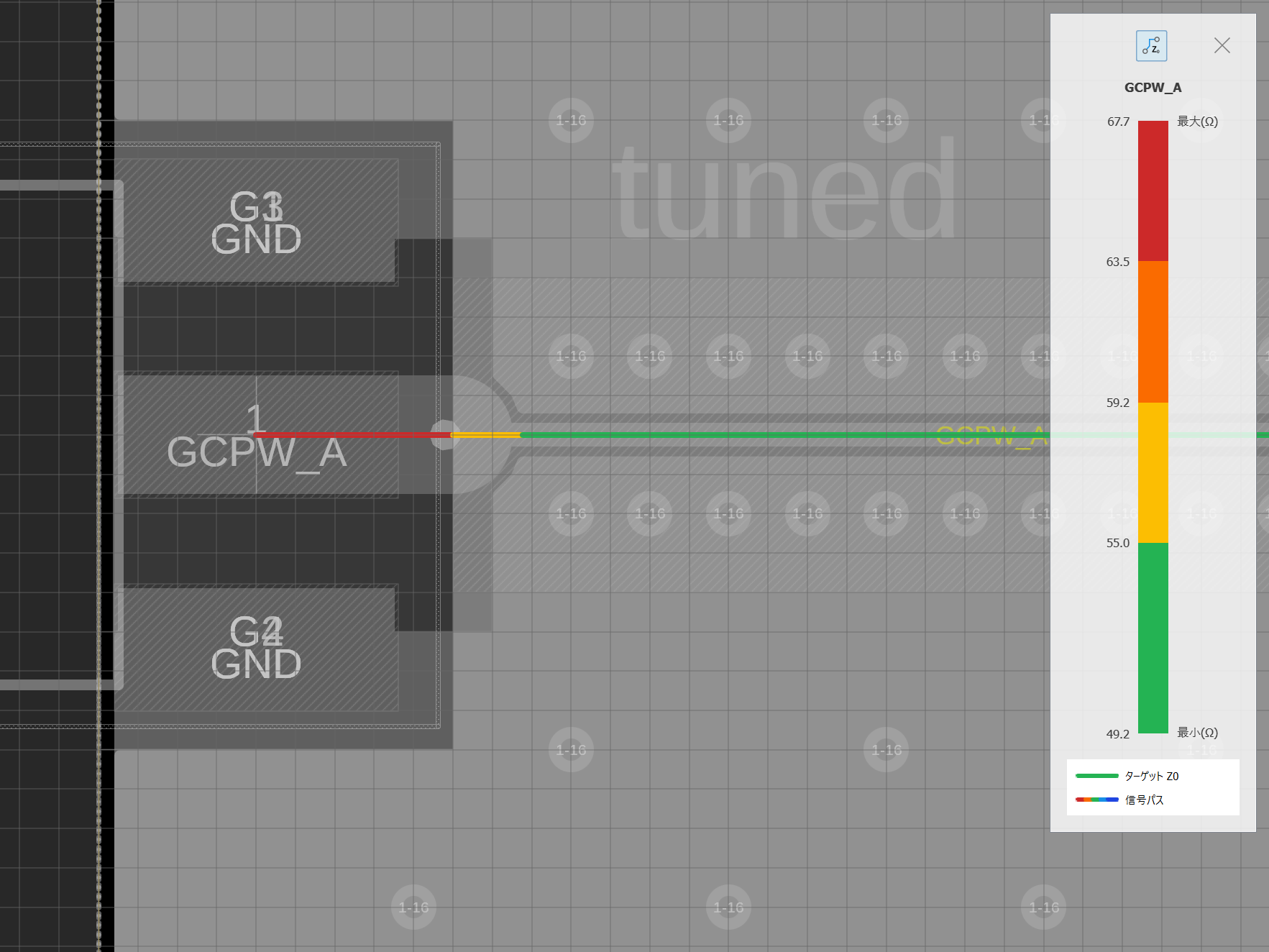

実際↓のようにこの線路幅ではかなり特性インピーダンスが下がります.

これをなんとかするために工夫をこらします.

とりあえず線路脇のGNDをどかしてMSLっぽく見える感じにしました.

なにもしないよりはやや改善されていすが,今回L1-L2層間が0.2104 mmと薄いためそこまで特性インピーダンスは変わりません.

ということで裏面GNDであるL2を一部カットアウトします↓.更に,実はL2だけでは微妙だったためL3もコネクタ下のGNDを抜き,L1-L4でMSLに見えるように修正しました.

このときの解析結果は以下のようになります.MSLに見せたパッド部分は良いのですがMSL-GCPWのトランジション部分が高インピーダンスになっています.

抜きすぎも良くないということですね……これもうわかんねぇな.

ということで電界の気持ちに寄り添った設計を心がけ,調整したところ以下のようになりました.

この解析機能をどこまで信用して良いのかまだあまりわかっていないのですが,長さ1 mm未満の区間で+7.2 Ωならまあ良いかなという感じです.

4.3. コネクタ芯線の影響を考慮する

さて,↑ではフットプリント周辺のGNDの配置をいいかんじに工夫してパッド部分の特性インピーダンスを50 Ωに,またパッド(ほぼMSLモード)とGCPWのトランジション部分でもなるべくインピーダンスギャップが生じないように設計しました. しかし,実際にはこのパッドの上にコネクタのセンターピンを乗せ,ハンダ付けするため,これよりも更に特性インピーダンスが下がることが予想されます. この影響について3次元電磁界シミュレータ(HFSSとか)でも確認はしているのですが,ピンの位置ズレやハンダの盛り具合などのモデリングによって値がバラつくため定量的評価は難しいかなと感じています. そこで今回はピンの影響を考慮せず50 Ωに整合し試作→実測のTDRから必要な補正量を見積るという流れを取ろうと考えました.が……

そう考えていた時代もあったのですが基板を発注する際,ここまで基板厚0.8 mmで設計していたのに対し,1.6 mmで注文するというミスを犯してしまいました.

このとき層構成で変わるのはL2-L3間のコア材のみで,L1-L2間のプリプレグは同一です.そのためGCPW部分の特性インピーダンスは変化しません.

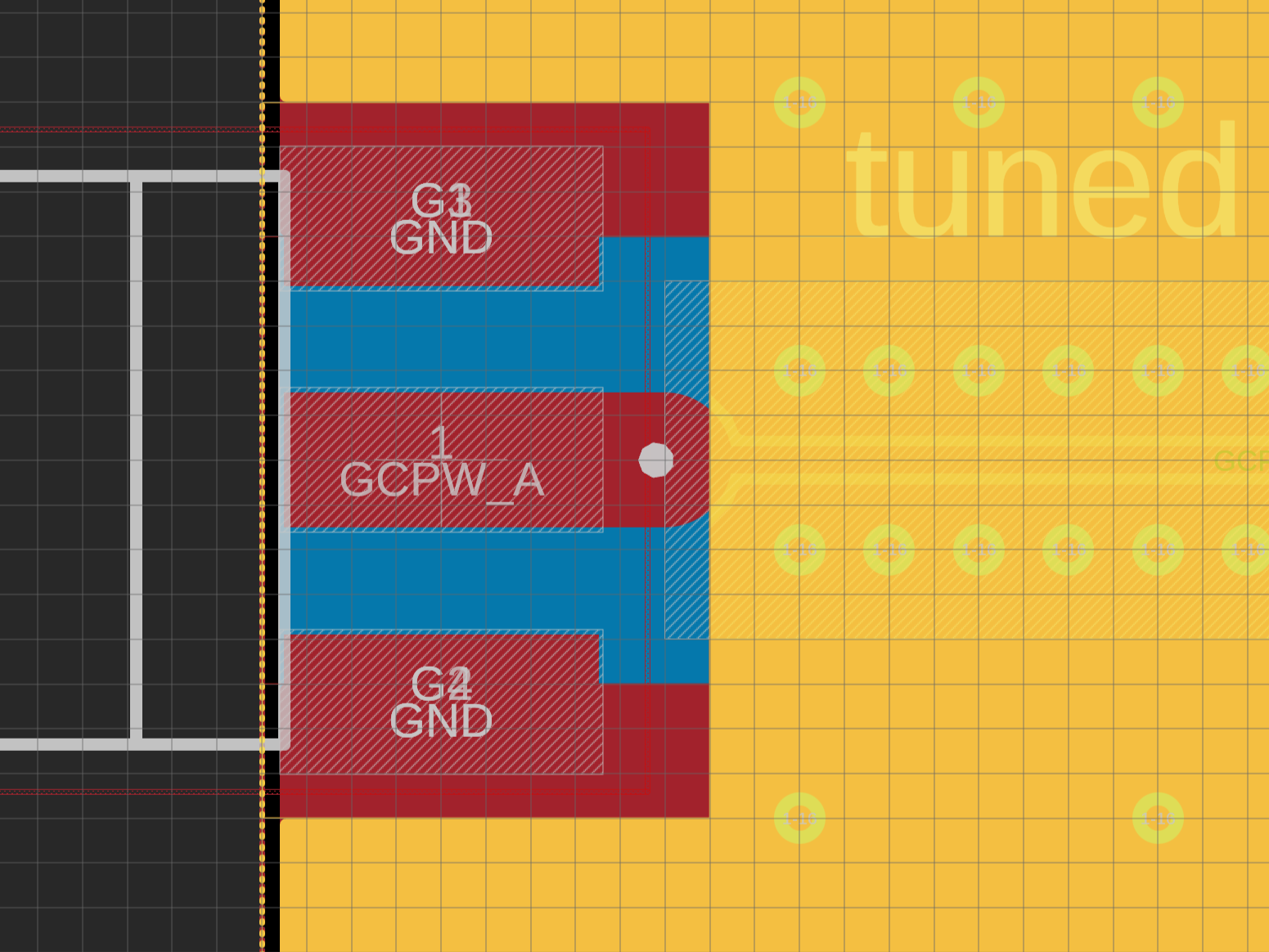

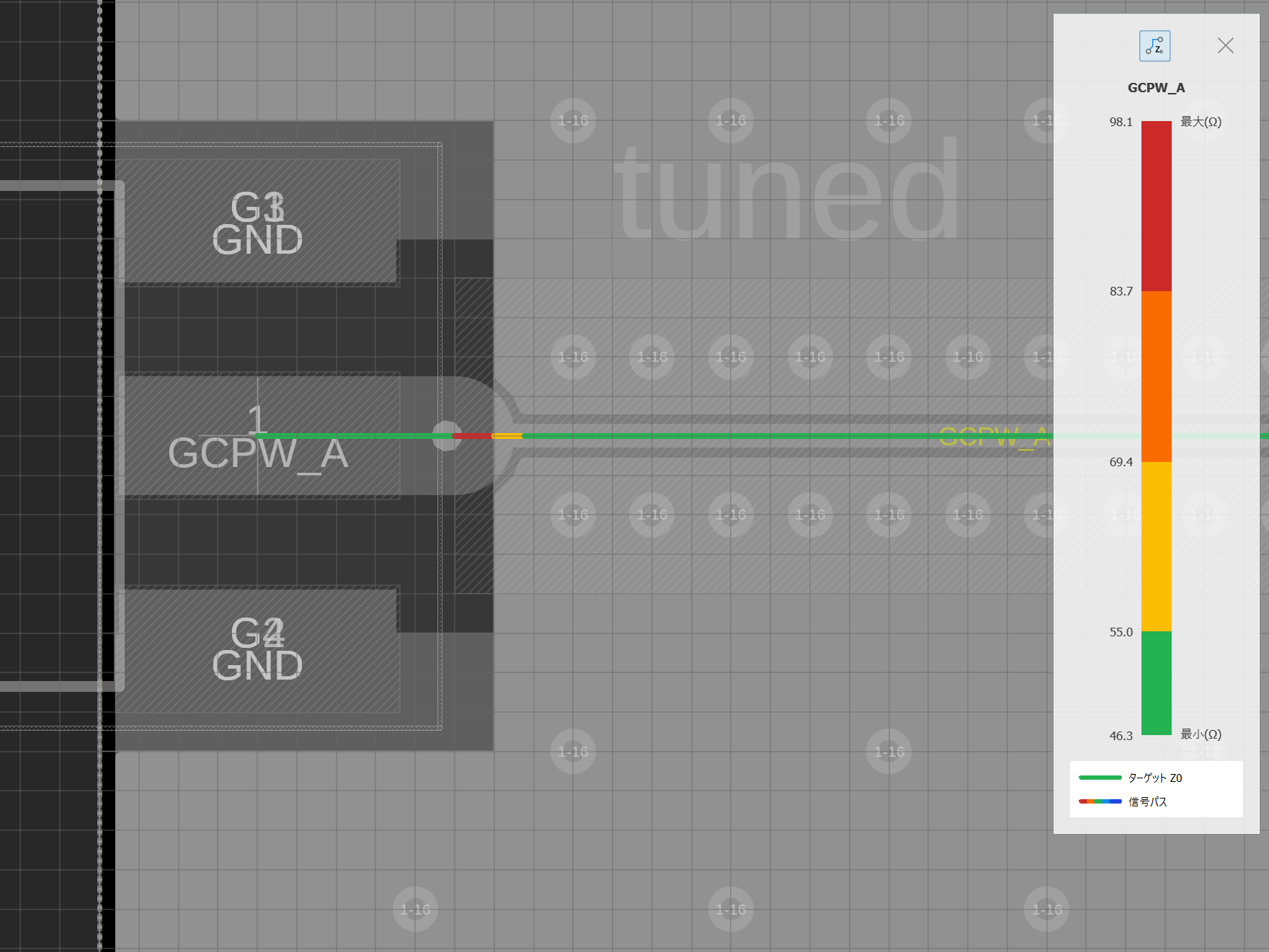

一方で内層のGNDを抜いていたコネクタ部分に関してはコア材の厚みが0.25 mmから1.065 mmに増した分,GNDが遠くなり以下のように特性インピーダンスが十数 Ωほど高くなります.

センターピンの影響を考えると若干特性インピーダンスを高く設計しておいた方が良いのは確かですが,はたしてこのミスは吉と出るのか凶と出るのか……

5. 実測

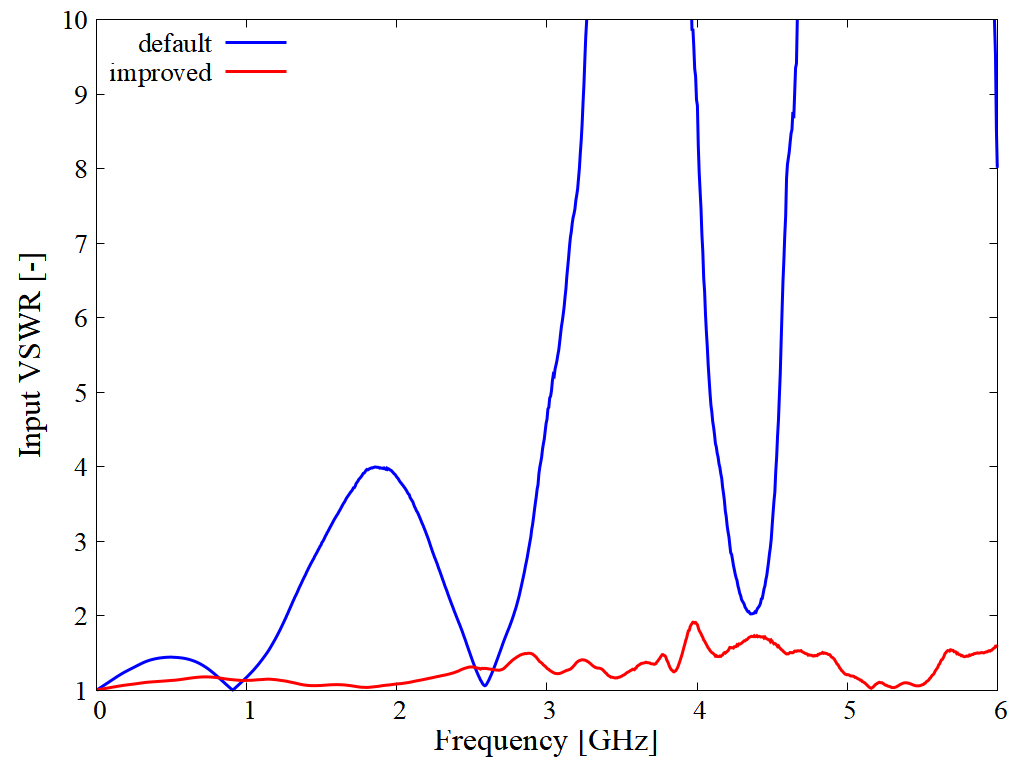

以下のように改善前後の回路の片端を終端して入力VSWRを比較します.

どうやら基板厚を間違えたのが結果的にちょうど良い感じになっていそうな気がします.

改善前の回路はGHzオーダーの周波数では反射が大きくお話になりませんが,改善後は6 GHzまでVSWR<2を保っています.

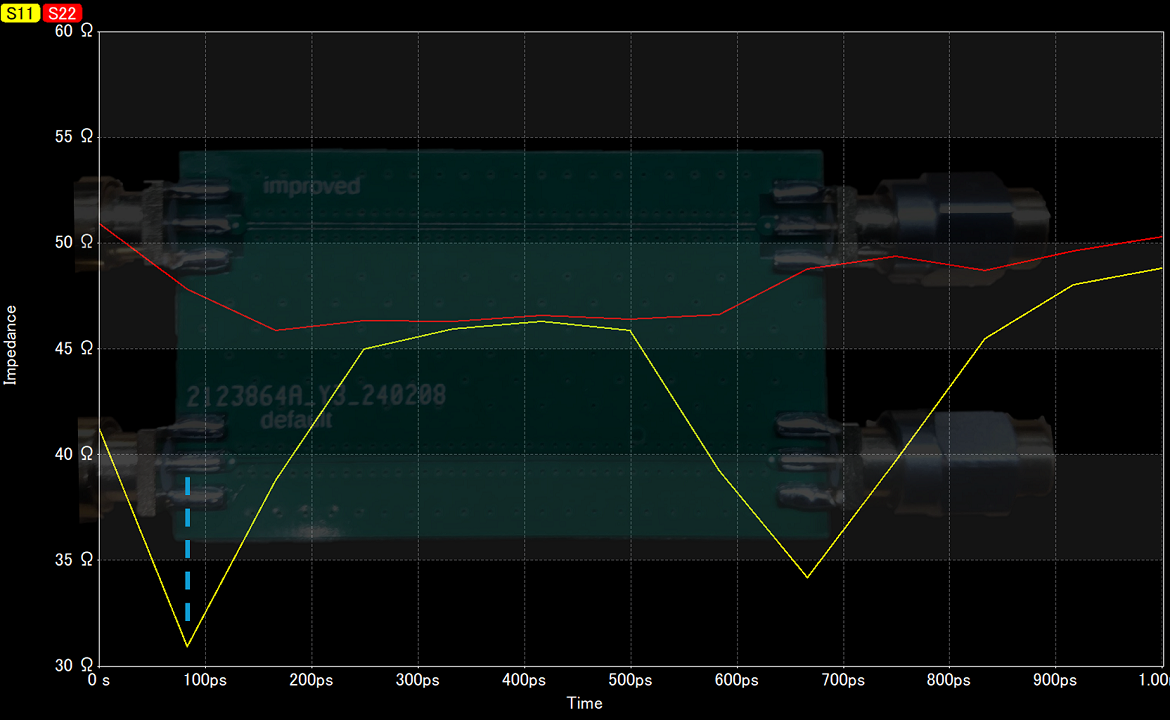

これらのTDR(Lowpass Step→Impedance)の特性は以下のようになります.

なんとなくイメージしやすい用にうっすらと対応する回路の画像を入れています.

黄色線で示した改善前と比較して,赤線の改善後の方はコネクタ接続部(水色の破線部分)でのインピーダンスの落ち込みが抑えられていることがわかります.

結果としてセンターピンの影響を考えるとやはりパッド部分は高インピーダンスぎみで設計すべきなようです.

またコネクタ取付部(100 psの手前らへん)よりも後で更にインピーダンスが下がっているような結果から,どうやらGCPW部分の特性インピーダンスが50 Ωより低くなっているような気がします.

これは,線路を設計する際にレジスト(solder mask)の\(\varepsilon_\mathrm{r}\)を考慮していないことが一つの要因かと思います7.

また以下のように未使用の線路を終端し,通過特性も評価しました.

この結果からもコネクタ部分の工夫で大きく特性が改善されていることがわかるかと思います.

この改善後の特性なら6 GHzでもまあなんとか使い物になるかな?といった印象です.

6. まとめ

ここでは安価なエッジマウントSMAコネクタとPCB上の伝送線路の接続について述べました. 何も考えず,CADについてくるライブラリのフットプリントのまま使うと反射が大きく, UHFの上のほうではもはや使い物になりません. フットプリントの寄生キャパシタンスおよびコネクタ芯線の影響を考慮して改善を行ったパターンではUHF帯あたりまで反射を-20 dB程度に抑え,6 GHz付近においても反射を- 10 dB以下に保つことができました. しかし今回の検証結果はまだ最適値では無い可能性が高く,SMAコネクタの上限である18 GHzまで伸ばすには更なる最適化が必要かと思います.

なんにせよSMAコネクタが18 GHzまで使えるからといって適当に接続してしまうとコネクタや回路のせっかくの性能を生かすことができません. 少なくとも1 GHzを越えるような高周波帯においてSMAコネクタを使うときはコネクタ-PCB間のトランジションについて適切に設計を行う必要があります. 近頃マイクロ波帯で動作する便利なMMICが出回り,巷ではそれらを基板に実装し,コネクタを付けたモジュールが安価に出回っていますが,そういったものを購入する際はコネクタ周りがどう設計されているかよく確認することをお勧めします.

Footnotes:

IEC-6119-15:2021

5 GHzを越えたあたりで反射が0 dBを越えてるように見えます.これは校正キットの補正値がややズレているのが原因で,お金があれば改善したいな……とは思っています.

手元には1 M~6 GHzまでの測定データがありますが,まずDC-1 MHzまでのデータを外挿し(低周波帯の反射は非常に小さいので適当に外挿してもそんなに問題無い), その後周波数応答がエルミート性であると信じて負の周波数領域に折り返します. これにステップ関数を乗じて逆フーリエ変換することで時間領域のステップ応答が求まり,更に反射係数と入力インピーダンスの関係式から換算することで時間-インピーダンスのグラフを得ることができます. 実際には適当に設定してボタンを押せばVNAが勝手にやってくれます.

- Würth Elektronik, "Coaxial PCB Connector PCB-Transmission Line Design Guide, " Application Note, ANE012b, 2021.

- Southwest Microwave, "Utilizing Time Domain (TDR) Test Methods For Maximizing Microwave Board Performance," Technical Articles, 2018.

普段,電子回路CADとしてAutodeskのFusion 360(かつてのEagle)を使っているのですが,最近Signal Integrity Extensionというものが使えるようになりました. Ansysの電磁界解析機能を搭載とのことですが解析結果などを見るに2D Extractorのように断面構造の(準)静電磁界を解析しているようです. なかなか便利ですが以下の点はまだまだ発展途上だと感じています.

- 宣伝文句では"カップリングの問題"と書いていますが現時点では結合線路の偶,奇モードインピーダンスなどは計算できない

- →解析対象以外の線路はGNDとして扱っているっぽい(つまり\(C_\mathrm{m},\ L_\mathrm{m}\)を0とした時の\(Z_0\))

- 部品ライブラリのfootprintの導体は無視される

- →パッドの上に同じ幅の信号線を乗せてあげると正しい結果が得られる

こちら教育機関ユーザーの学習や研究目的であれば教育機関ライセンスに含まれるので,Eagle派の学生の方は是非使ってみてください.

MSLではあまりレジストの影響を受けないのですが,コプレーナ線路の場合は信号線と両側のGNDの間に誘電体が入ることになるので結構特性インピーダンスが変わります. レジストの\(\varepsilon_\mathrm{r}\)を考慮して設計すれば良いのですが, 基板材料と比べて提供されているデータがラフであり,また銅箔や基板厚と比べるとレジスト厚はかなりばらつきが大きいことや,G-S間の溝にどの程度レジストが埋まるかといった点は性格なコントロールが難しいためこのような場合はレジストを掛けずに線路を剥き出しにする(錆びるのでENIGとか掛ける)のが良いと思います.